Updated on Mar 21, 2026

The Peripheral Component Interconnect (PCI) architecture has become the most common method used to extend PCs for add-on adapters over the years. Originally intended for personal computer systems, the PCI architecture has penetrated into virtually every computing platform category, including servers, storage, communications, and a wide range of embedded control applications.

From its early incarnation as a 32-bit 33MHz interconnect, it has been expanded to offer higher speeds (currently in widespread use at 64-bit 133MHz, with faster versions on the way).

Most importantly, each advancement in PCI bus speed and width provided backward software compatibility, allowing designers to leverage the broad code base. Compared to the progress made every year in other areas of computer technology such as processors and video cards, computer I/O system technology would seem to be standing still… in fact it is. Since the introduction of the original PCI bus back in the early 90's, very little has changed in the way that data is handled inside the computer. The PCI local bus is a high performance bus for interconnecting chips, expansion boards and processor/memory subsystems.

The PCI bus has served well for the last 10 years and it will play a major role in the next few years. However, today's and tomorrow's processors and I/O devices are demanding much higher I/O bandwidth than PCI 2.2 or PCI-X can deliver and it is time to engineer a new generation of PCI to serve as a standard I/O bus for future generation platforms. There have been several efforts to create higher bandwidth buses and this has resulted in the PC platform supporting a variety of application-specific buses alongside the PCI I/O expansion bus.

Today's software applications are more demanding of the platform hardware, particularly the I/O subsystems. Streaming data from various video and audio sources are now commonplace on the desktop and mobile machines and there is no baseline support for this time-dependant data within the PCI 2.2 or PCI-X specifications. Applications such as video-on-demand and audio re-distribution are putting real-time constraints on servers too. Many communications applications and embedded-PC control systems also process data in real-time. Today's platforms, (Figure 1.1), must also deal with multiple concurrent transfers at ever-increasing data rates. [4]

Data needs to be "tagged" so that an I/O system can prioritize its flow throughout the platform, since all data cannot be treated equal in real time computing. High performance peripherals and adapters developed, demanded high speed data transfer and a third generation I/O bus had to be developed. As successful as the PCI architecture has become, there is a limit to what can be accomplished with a multi-drop, parallel shared bus interconnect technology. [1] Issues such as clock skew, high pin count, trace routing restrictions in printed circuit boards (PCB), bandwidth and latency requirements, physical scalability, and the need to support Quality of Service (QoS) within a system for a wide variety of applications lead to the definition of the PCI Express™ architecture.

PCI Express is the natural successor to PCI, and was developed to provide the advantages of a state-of-the-art, high-speed serial interconnect technology and packet based layered architecture, but maintain backward compatibility with the large PCI software infrastructure. The key goal was to provide an optimized and universal interconnect solution for a great variety of future platforms, including desktop, server, workstation, storage, communications and embedded systems.

Approved as a standard on April 17 2002, PCI-Express is intended to be an evolutionary upgrade to the existing PCI bus [7]. It will maintain complete hardware and software compatibility with all recent PCI devices. It is expected that PCI will coexist in many platforms to support today's lower bandwidth applications until a compelling need, such as a new form factor, causes a full migration to a fully PCI Express based platform.

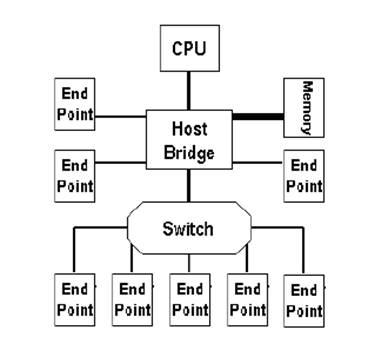

The PCI Express, also called the Third Generation I/O (3GIO) architecture is the next generation chip-to-chip interconnect for computing [4]. Recent advances in high-speed low-pin-count, point-to-point technologies offer an attractive alternative for major bandwidth improvements. A PCI Express topology contains a Host Bridge and several endpoints (the I/O devices). Multiple point-to-point connections introduce a new element, the switch, into the I/O system topology. (Figure 2.1). The switch is shown as a separate logical element but it could be integrated into a host bridge component

The multiple, similar parallel buses of today’s platform are replaced with PCI Express links with one or more lanes. Each link is individually scalable by adding more lanes so that additional bandwidth may be applied to those links where it is required – such as graphics in the desktop platform and bus bridges (e.g. PCI Express-to-PCI-X) in the server platform. Table 2.1 presents the peak bandwidth of the PCI, PCI-X, and AGP buses.

The PCI-Express bus will no longer be a single parallel data bus through which all data is routed at a set rate [3]. Rather, an assembly of serial, point-to-point wired, individually clocked ‘lanes' each consisting of two pairs of data lines will carry data upstream and downstream. As the technology goes to market, each of these lanes should be capable of a 2.5Gb/s data rate in each direction. The overall sustained transfer rate roughly equals 200MB/S

PCI Express is expected to be deployed initially in desktop and server systems [1]. These computers typically utilize a chipset solution that includes one or more microprocessors and two types of special interconnect devices, called northbridges and southbridges. Northbridges connect the CPU with memory, graphics and I/O. Southbridges connect to standardized I/O devices such as hard disk drives, networking modules or devices, and often PCI expansion slots.

Typical use of PCI Express in a desktop application is shown in figure 2.2. The PCI Express ports come directly out of the northbridge, and are bridged to PCI slots that are used for legacy plug-in cards. In some implementations the PCI Express interconnections will be completely hidden from the user behind PCI bridges, and in other implementations there will be PCI Express slots in a new PCI Express connector form factor.

| Are you interested in this topic.Then mail to us immediately to get the full report.

email :- contactv2@gmail.com |