Published on Nov 30, 2023

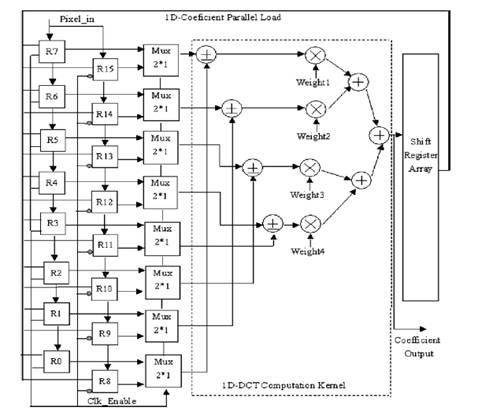

This paper presents a cost-effective 2-D-discrete cosine transform (DCT) architecture based on the fast row/column decomposition algorithm. We propose a new schedule for 2-D-DCT computing to reduce the hardware cost.

With this approach, the transposed memory can be simplified using shift-registers for the data transposition between two 1-D-DCT units.

A special shift cell with MOS circuit is designed by using the energy transferring methodology. The memory size can be greatly reduced, and the address generator and its READ/WRITE control all can be saved.

For an 8 8-block transformation, the number of transistors is only 4 k for the shift-register array. The maximum frequency of shift-operation can achieve about 120 MHz, when implemented by 0.35- m technology

This paper presents a cost-effective DCT architecture for video coding applications. The 2-D-DCT processor is realized with a particular schedule consisting of 1-D-DCT core and the shift-register array.

The shift-registers array can perform data transposition with serial-in/parallel-out structure based on pseudo capacitor technique. The shift-register based transposition can reduce the control-overhead since the address generator and decoder for memory access can be removed.

Comparison with the transposition-based DCT chips, the memory size and the full 2-D-DCT complexity can be reduced about a factor of 1/8 and 1/2, respectively. With low circuit complexity and control overhead, the proposed DCT IP can provide a cost-effective solution for video encoder

VHDL

Simulation: Modelsim 6.2g

Synthesis: XILINX 7.1 i